## **User Manual**

## **PCI-7031**

Intel<sup>®</sup> Atom<sup>™</sup> Dual-Core D510/ Fanless N450 CPU, PCI Half-size SBC with on-board DDR2 / VGA / LVDS / Dual-GbE / SATA / COM

## Copyright

The documentation and the software included with this product are copyrighted 2009 by c@ Á a) ~a&c |^|. All rights are reserved. V@ Á a) ~a&c |^| reserves the right to make improvements in the products described in this manual at any time without notice.

No part of this manual may be reproduced, copied, translated or transmitted in any form or by any means without the prior written permission of @Á æ ~æc |^|.

Information provided in this manual is intended to be accurate and reliable. However, @Á æ ~æc |^| assumes no responsibility for its use, nor for any infringements of the rights of third parties, which may result from its use.

## **Acknowledgements**

PICMG<sup>®</sup> and the PICMG<sup>®</sup> logos are trademarks of the PCI Industrial Computers Manufacturers Group.

All other product names or trademarks are properties of their respective owners.

#### **Certifications**

CE

FCC Class A

Part No. 2002703101 Printed in Taiwan Edition 2 December 2009

#### A Message to the Customer

#### **Technical support**

We want you to get the maximum performance from your products. So if you run into technical difficulties, we are here to help. For the most frequently asked questions, you can easily find answers in your product documentation. These answers are normally a lot more detailed than the ones we can give over the phone.

So please consult this manual first. If you still cannot find the answer, gather all the information or questions that apply to your problem, and with the product close at hand, call your dealer. Our dealers are well trained and ready to give you the support you need to get the most from your products. In fact, most problems reported are minor and are able to be easily solved over the phone.

In addition, free technical support is available from [ \* | engineers every business day. We are always ready to give advice on application requirements or specific information on the installation and operation of any of our products.

## **Product Warranty (2 years)**

V@Á æj æšc '^ warrants to you, the original purchaser, that each of its products 引為free from defects in materials and workmanship for two years from the date [ 本 h chase.

If you think you have a defective product, follow these steps:

- Collect all the information about the problem encountered. (For example, CPU speed, other hardware and software used, etc.) Note anything abnormal and list any onscreen messages you get when the problem occurs.

- 2. Call your dealer and describe the problem. Please have your manual, product, and any helpful information readily available.

- 3. If your product is diagnosed as defective, obtain an RMA (return merchandise authorization) number from your dealer. This allows us to process your return more quickly.

- 4. Carefully pack the defective product, a fully-completed Repair and Replacement Order Card and a photocopy proof of purchase date (such as your sales receipt) in a shippable container. A product returned without proof of the purchase date is not eligible for warranty service.

- 5. Write the RMA number visibly on the outside of the package and ship it prepaid to your dealer.

Before you begin installing your single board computer, please make sure that the following materials have been shipped:

If any of these items are missing or damaged, contact your distributor or sales representative immediately.

We have carefully inspected the PCI-7031 mechanically and electrically before shipment. It should be free of marks and scratches and in perfect working order upon receipt.

As you unpack the PCI-7031, check it for signs of shipping damage. (For example, damaged box, scratches, dents, etc.) If it is damaged or it fails to meet the specifications, notify our service department or your local sales representative immediately. Also notify the carrier. Retain the shipping carton and packing material for inspection by the carrier. After inspection, we will make arrangements to repair or replace the unit.

## **Initial Inspection**

Before you begin installing your single board computer, please make sure that the following materials have been shipped:

| 1 PCI-7031D(N)-S6A1E single board computer                |                     |

|-----------------------------------------------------------|---------------------|

| 1 CPU Cooler for Atom D510 CPU (Only Available for D SKU) | P/N: 1960046526N001 |

| 1 PCI-7031 Startup Manual                                 |                     |

| 1 CD with driver utility and manual (in PDF format)       |                     |

| 1 FDD cable                                               | P/N: 1700340640     |

| 1 Ultra ATA 66/100 HDD cables                             | P/N: 1701400452     |

| 2 Serial ATA HDD data cable                               | P/N: 1700003194     |

| 2 Serial ATA HDD power cable                              | P/N: 1703150102     |

| 1 Printer (parallel) port cable kit                       | P/N: 1701260301     |

| 1 Dual COM ports cable kit                                | P/N: 1700008762     |

| 1 ATX Feature Cable                                       | P/N: 1700002343     |

| 1 4-Port USB cable kit                                    | P/N: 1700008887     |

| 1 Y cable for PS/2 keyboard and PS/2 mouse                | P/N: 1700060202     |

| 1 AT/ATX PSU 20-Pin to 12-Pin Cable Kit                   | P/N: 1700000265     |

| 1 Jumper Pack                                             | P/N: 9689000068     |

| 1 Warranty card                                           |                     |

|                                                           |                     |

If any of these items are missing or damaged, contact your distributor or sales representative immediately.

We have carefully inspected the PCI-7031 mechanically and electrically before shipment. It should be free of marks and scratches and in perfect working order upon receipt.

As you unpack the PCI-7031, check it for signs of shipping damage. (For example, damaged box, scratches, dents, etc.) If it is damaged or it fails to meet the specifications, notify our service department or your local sales representative immediately. Also notify the carrier. Retain the shipping carton and packing material for inspection by the carrier. After inspection, we will make arrangements to repair or replace the unit.

#### Note!

Using PCI-7031D's proprietary CPU cooler included in its package is a must. Other brands of CPU coolers are NOT compatible with PCI-7031. PCI-7031N is of fanless CPU type and does not need installing a CPU cooler by user.

## **Verified Memory List**

| Brand          | Size      | Speed       | Туре           | ECC | Vendor PN                       |             | Memory                               |

|----------------|-----------|-------------|----------------|-----|---------------------------------|-------------|--------------------------------------|

|                | 256<br>MB | DDR2<br>667 | SODIMM<br>DDR2 | N   | TS32MSQ64V6M                    | Ж           | Hynix HY5PS121621B FP-Y5<br>(32x16)  |

| Tran-<br>scend | 512<br>MB | DDR2<br>667 | SODIMM<br>DDR2 | N   | TS6QSJ23002-6S/<br>TS64MSQ64V6J | Á<br>Á<br>Á | SAMSUNG K4T51083QC ZCE6 (64x8)       |

|                | 512<br>MB | DDR2<br>667 | SODIMM<br>DDR2 | N   | Hynix<br>HY5PS121621B<br>FP-Y5  | Á           | Hynix HY5PS121621B FP-Y5 (32x16)     |

|                | 1 GB      | DDR2<br>667 | SODIMM<br>DDR2 | N   | TS128MSQ64V6J                   | ÁÁ          | SAMSUNG K4T51083QC ZCE6<br>(64x8)    |

|                | 2 GB      | DDR2<br>667 | SODIMM<br>DDR2 | N   | TS5QSU27300-6M                  | ÁÁ<br>ÁÁ    | Micron D9HNL (128x8)                 |

| Anger          | 512<br>MB | DDR2<br>667 | SODIMM<br>DDR2 | N   | 78.92G63.422                    | ÁÁ          | ELPIDA E5108AG-6E-E (64x8)           |

| Apacer         | 1 GB      | DDR2<br>667 | SODIMM<br>DDR2 | N   | 78.02G63.423                    | ÁÁ<br>Á     | ELPIDA E5108AGBG-6E-E<br>(64x8)      |

|                | 256<br>MB | DDR2<br>667 | SODIMM<br>DDR2 | N   | NA                              | Á           | ELPIDA E5116AF-6E-E (32x16)          |

|                | 512<br>MB | DDR2<br>667 | SODIMM<br>DDR2 | N   | NA                              |             | ELPIDA E5108AGBG-6E-E<br>(64x8)      |

|                | 1 GB      | DDR2<br>667 | SODIMM<br>DDR2 | N   | NA                              |             | ELPIDA E5108AGBG-6E-E<br>(64x8)      |

| DCI            | 2 GB      | DDR2<br>667 | SODIMM<br>DDR2 | N   | NA                              |             | ELPIDA E1108ACSE-6E-E<br>(128x8)     |

| DSL            | 1 GB      | DDR2<br>800 | SODIMM<br>DDR2 | N   | TS64MSQ64V6M                    | Á           | Hynix HY5PS121621B FP-Y5<br>(32x16)  |

|                | 2 GB      | DDR2<br>800 | SODIMM<br>DDR2 | N   | TS256MSQ64V8U                   | Á           | Micron D9HNP (128x8)                 |

|                | 1 GB      | DDR2<br>800 | SODIMM<br>DDR2 | N   | NA                              |             | ELPIDA TWN E5108AHSE-8E-<br>E (64x8) |

|                | 2 GB      | DDR2<br>800 | SODIMM<br>DDR2 | N   | NA                              |             | ELPIDA JPN E1108ACSE-8E-E<br>(128x8) |

#### **Certification and Safety Instructions**

This device complies with the requirements in part 15 of the FCC rules: Operation is subject to the following two conditions:

- 1. This device may not cause harmful interference, and

- 2. This device must accept any interference received, including interference that may cause undesired operation

This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this device in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his/her own expense. The user is advised that any equipment changes or modifications not expressly approved by the party responsible for compliance would void the compliance to FCC regulations and therefore, the user's authority to operate the equipment.

Caution! There is a danger of a new battery exploding if it is incorrectly installed. Do not attempt to recharge, force open, or heat the battery. Replace the battery only with the same or equivalent type recommended by the manufacturer. Discard used batteries according to the manufacturer's instructions.

| Cnapter | 1                                                            | Hardware Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | I                                                        |

|---------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|         | 1.1                                                          | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2                                                        |

|         | 1.2                                                          | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                          |

|         | 1.3                                                          | Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |

|         |                                                              | 1.3.1 System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                          |

|         |                                                              | 1.3.2 Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                          |

|         |                                                              | 1.3.3 Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                          |

|         |                                                              | 1.3.4 Graphic interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                          |

|         |                                                              | 1.3.5 Ethernet LAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4                                                        |

|         |                                                              | 1.3.6 Industrial features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                          |

|         |                                                              | 1.3.7 Mechanical and environmental specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          |

|         | 1.4                                                          | Jumpers and Connectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                          |

|         |                                                              | Table 1.1: Jumper descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |

|         |                                                              | Table 1.2: Connector descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          |

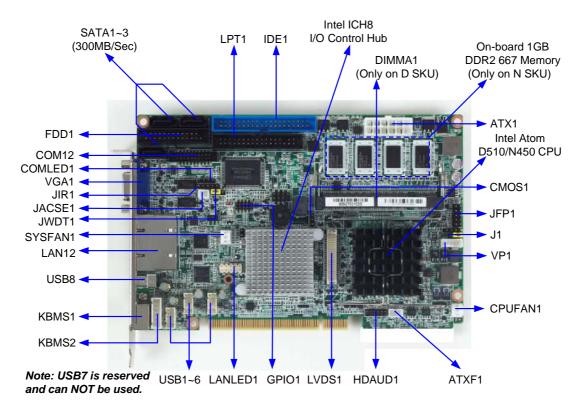

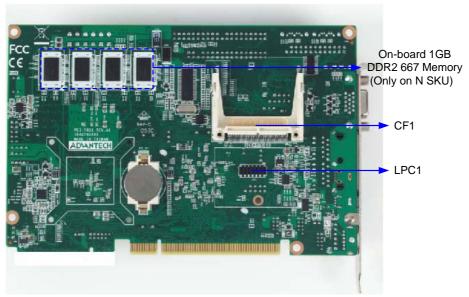

|         | 1.5                                                          | Board Layout: Jumper and Connector Locations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                          |

|         |                                                              | Figure 1.1 Board Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                          |

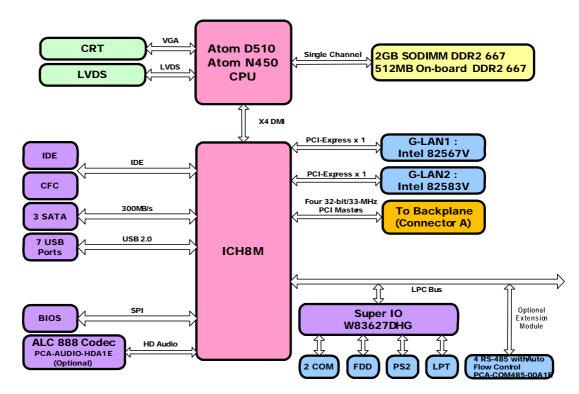

|         | 1.6                                                          | PCI-7031 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                          |

|         |                                                              | Figure 1.2 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                          |

|         | 1.7                                                          | Safety Precautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                          |

|         | 1.8                                                          | System Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                          |

|         | 1.9                                                          | Memory Installation Procedures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |

|         | 1.10                                                         | Processor Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                          |

|         | 1.11                                                         | CPU Cooler Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10                                                       |

| Chapter | 2                                                            | <b>Connecting Peripherals &amp; Jumper</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          |

| •       |                                                              | Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _11                                                      |

|         |                                                              | 994411199                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                          |

|         |                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                          |

|         | 2.1                                                          | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12                                                       |

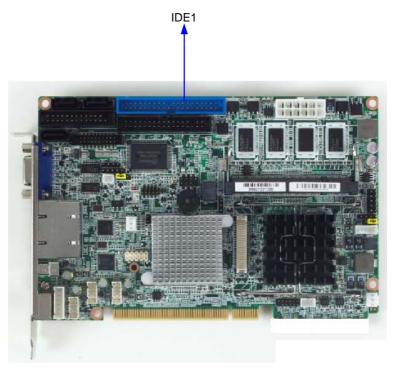

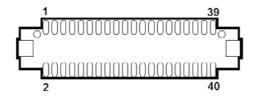

|         | 2.1<br>2.2                                                   | IntroductionIDE Connector (IDE1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |

|         |                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12                                                       |

|         |                                                              | IDE Connector (IDE1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12<br>12                                                 |

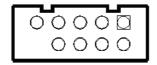

|         | 2.2                                                          | IDE Connector (IDE1)Figure 2.1 PCI-7031 IDE1 location                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12<br>12<br>13                                           |

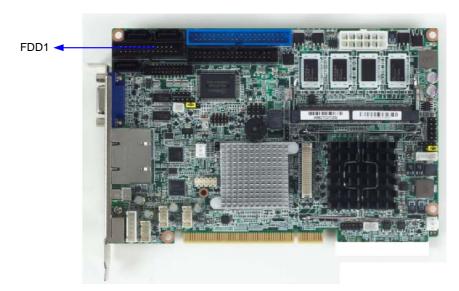

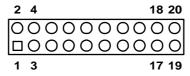

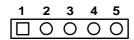

|         | 2.2                                                          | IDE Connector (IDE1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12<br>12<br>13<br>13                                     |

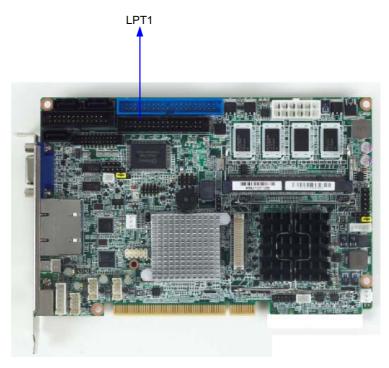

|         | 2.2                                                          | IDE Connector (IDE1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12<br>12<br>13<br>13                                     |

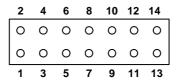

|         | 2.2                                                          | IDE Connector (IDE1) Figure 2.1 PCI-7031 IDE1 location Floppy Drive Connector (FDD1) Figure 2.2 PCI-7031 FDD1 location Parallel Port (LPT1) Figure 2.3 PCI-7031 LPT1 location VGA Connector (VGA1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12<br>13<br>13<br>14<br>14                               |

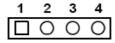

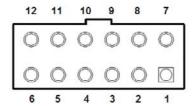

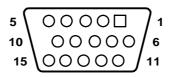

|         | 2.2<br>2.3<br>2.4                                            | IDE Connector (IDE1) Figure 2.1 PCI-7031 IDE1 location Floppy Drive Connector (FDD1) Figure 2.2 PCI-7031 FDD1 location Parallel Port (LPT1) Figure 2.3 PCI-7031 LPT1 location VGA Connector (VGA1) Figure 2.4 VGA Connector (VGA1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12<br>13<br>13<br>14<br>15                               |

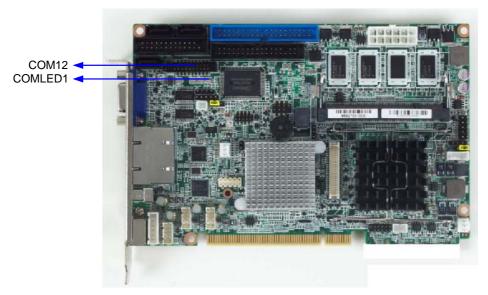

|         | 2.2<br>2.3<br>2.4                                            | IDE Connector (IDE1)  Figure 2.1 PCI-7031 IDE1 location  Floppy Drive Connector (FDD1)  Figure 2.2 PCI-7031 FDD1 location  Parallel Port (LPT1)  Figure 2.3 PCI-7031 LPT1 location  VGA Connector (VGA1)  Figure 2.4 VGA Connector (VGA1)  Serial Ports (COM12)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12<br>13<br>13<br>14<br>14<br>15<br>15                   |

|         | <ul><li>2.2</li><li>2.3</li><li>2.4</li><li>2.5</li></ul>    | IDE Connector (IDE1) Figure 2.1 PCI-7031 IDE1 location Floppy Drive Connector (FDD1) Figure 2.2 PCI-7031 FDD1 location  Parallel Port (LPT1) Figure 2.3 PCI-7031 LPT1 location  VGA Connector (VGA1) Figure 2.4 VGA Connector (VGA1)  Serial Ports (COM12) Figure 2.5 Serial Ports (COM12)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12<br>13<br>13<br>14<br>15<br>15<br>15                   |

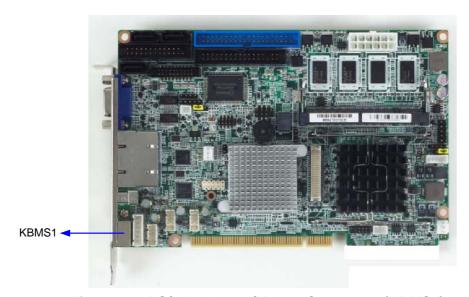

|         | <ul><li>2.2</li><li>2.3</li><li>2.4</li><li>2.5</li></ul>    | IDE Connector (IDE1) Figure 2.1 PCI-7031 IDE1 location Floppy Drive Connector (FDD1) Figure 2.2 PCI-7031 FDD1 location  Parallel Port (LPT1) Figure 2.3 PCI-7031 LPT1 location  VGA Connector (VGA1) Figure 2.4 VGA Connector (VGA1)  Serial Ports (COM12) Figure 2.5 Serial Ports (COM12)  PS/2 Keyboard/Mouse Connector (KBMS1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12 13 13 14 15 15 15 15                                  |

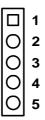

|         | 2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7                       | IDE Connector (IDE1) Figure 2.1 PCI-7031 IDE1 location Floppy Drive Connector (FDD1) Figure 2.2 PCI-7031 FDD1 location Parallel Port (LPT1) Figure 2.3 PCI-7031 LPT1 location VGA Connector (VGA1) Figure 2.4 VGA Connector (VGA1) Serial Ports (COM12) Figure 2.5 Serial Ports (COM12) PS/2 Keyboard/Mouse Connector (KBMS1) Figure 2.6 PS/2 Keyboard/Mouse Connector (KBMS1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12 13 14 15 15 15 15 16                                  |

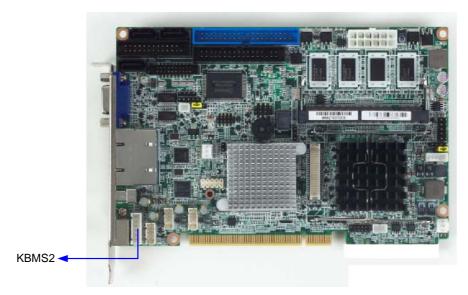

|         | 2.2<br>2.3<br>2.4<br>2.5<br>2.6                              | IDE Connector (IDE1) Figure 2.1 PCI-7031 IDE1 location Floppy Drive Connector (FDD1) Figure 2.2 PCI-7031 FDD1 location Parallel Port (LPT1) Figure 2.3 PCI-7031 LPT1 location VGA Connector (VGA1) Figure 2.4 VGA Connector (VGA1) Serial Ports (COM12) Figure 2.5 Serial Ports (COM12) PS/2 Keyboard/Mouse Connector (KBMS1) Figure 2.6 PS/2 Keyboard/Mouse Connector (KBMS1) External Keyboard Pin Header (KBMS2)                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12 13 14 15 15 15 16 16                                  |

|         | 2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8                | IDE Connector (IDE1) Figure 2.1 PCI-7031 IDE1 location Floppy Drive Connector (FDD1) Figure 2.2 PCI-7031 FDD1 location Parallel Port (LPT1) Figure 2.3 PCI-7031 LPT1 location VGA Connector (VGA1) Figure 2.4 VGA Connector (VGA1) Serial Ports (COM12) Figure 2.5 Serial Ports (COM12) PS/2 Keyboard/Mouse Connector (KBMS1) Figure 2.6 PS/2 Keyboard/Mouse Connector (KBMS1) External Keyboard Pin Header (KBMS2) Figure 2.7 External Keyboard Connector (KBMS2)                                                                                                                                                                                                                                                                                                                                                                                        | 12 13 14 15 15 15 16 16 16                               |

|         | 2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7                       | IDE Connector (IDE1) Figure 2.1 PCI-7031 IDE1 location Floppy Drive Connector (FDD1) Figure 2.2 PCI-7031 FDD1 location Parallel Port (LPT1) Figure 2.3 PCI-7031 LPT1 location VGA Connector (VGA1) Figure 2.4 VGA Connector (VGA1) Serial Ports (COM12) Figure 2.5 Serial Ports (COM12) PS/2 Keyboard/Mouse Connector (KBMS1) Figure 2.6 PS/2 Keyboard/Mouse Connector (KBMS1) External Keyboard Pin Header (KBMS2) Figure 2.7 External Keyboard Connector (KBMS2) CPU Fan Connectors (CPUFAN1)                                                                                                                                                                                                                                                                                                                                                           | 12 13 14 15 15 15 16 16 16 16                            |

|         | 2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9         | IDE Connector (IDE1) Figure 2.1 PCI-7031 IDE1 location  Floppy Drive Connector (FDD1) Figure 2.2 PCI-7031 FDD1 location  Parallel Port (LPT1) Figure 2.3 PCI-7031 LPT1 location  VGA Connector (VGA1) Figure 2.4 VGA Connector (VGA1)  Serial Ports (COM12) Figure 2.5 Serial Ports (COM12)  PS/2 Keyboard/Mouse Connector (KBMS1) Figure 2.6 PS/2 Keyboard/Mouse Connector (KBMS1)  External Keyboard Pin Header (KBMS2) Figure 2.7 External Keyboard Connector (KBMS2)  CPU Fan Connectors (CPUFAN1) Figure 2.8 CPU Fan Connectors (CPUFAN1)                                                                                                                                                                                                                                                                                                            | 12 13 14 15 15 15 16 16 16 17                            |

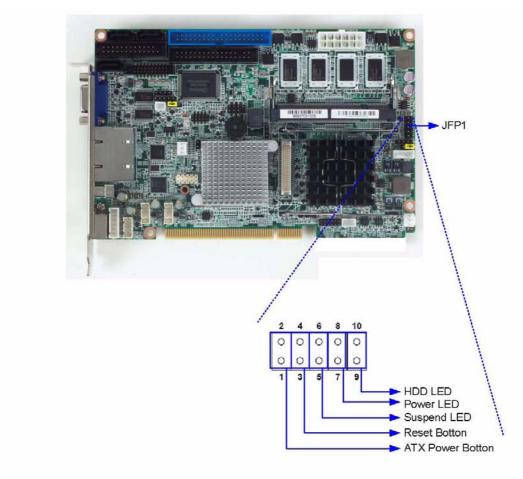

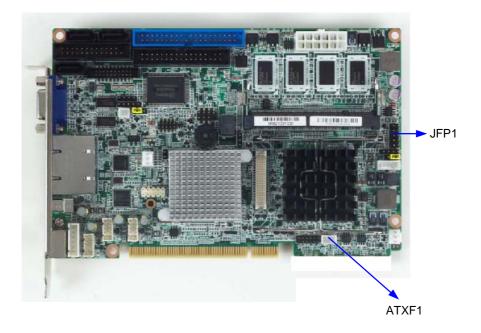

|         | 2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8                | IDE Connector (IDE1) Figure 2.1 PCI-7031 IDE1 location Floppy Drive Connector (FDD1) Figure 2.2 PCI-7031 FDD1 location Parallel Port (LPT1) Figure 2.3 PCI-7031 LPT1 location VGA Connector (VGA1) Figure 2.4 VGA Connector (VGA1) Serial Ports (COM12) Figure 2.5 Serial Ports (COM12) PS/2 Keyboard/Mouse Connector (KBMS1) Figure 2.6 PS/2 Keyboard/Mouse Connector (KBMS1) External Keyboard Pin Header (KBMS2) Figure 2.7 External Keyboard Connector (KBMS2) CPU Fan Connectors (CPUFAN1) Figure 2.8 CPU Fan Connectors (CPUFAN1) Front Panel Connectors (JFP1)                                                                                                                                                                                                                                                                                     | 12 13 14 15 15 15 16 16 16 17 17                         |

|         | 2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9         | IDE Connector (IDE1) Figure 2.1 PCI-7031 IDE1 location Floppy Drive Connector (FDD1) Figure 2.2 PCI-7031 FDD1 location  Parallel Port (LPT1) Figure 2.3 PCI-7031 LPT1 location  VGA Connector (VGA1) Figure 2.4 VGA Connector (VGA1) Serial Ports (COM12) Figure 2.5 Serial Ports (COM12)  PS/2 Keyboard/Mouse Connector (KBMS1) Figure 2.6 PS/2 Keyboard/Mouse Connector (KBMS1)  External Keyboard Pin Header (KBMS2) Figure 2.7 External Keyboard Connector (KBMS2)  CPU Fan Connectors (CPUFAN1) Figure 2.8 CPU Fan Connectors (CPUFAN1)  Front Panel Connectors (JFP1) Figure 2.9 Front Panel Connectors (JFP1)                                                                                                                                                                                                                                      | 12 13 14 15 15 15 16 16 17 17                            |

|         | 2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9         | IDE Connector (IDE1) Figure 2.1 PCI-7031 IDE1 location Floppy Drive Connector (FDD1). Figure 2.2 PCI-7031 FDD1 location.  Parallel Port (LPT1). Figure 2.3 PCI-7031 LPT1 location  VGA Connector (VGA1). Figure 2.4 VGA Connector (VGA1).  Serial Ports (COM12). Figure 2.5 Serial Ports (COM12).  PS/2 Keyboard/Mouse Connector (KBMS1). Figure 2.6 PS/2 Keyboard/Mouse Connector (KBMS1).  External Keyboard Pin Header (KBMS2). Figure 2.7 External Keyboard Connector (KBMS2).  CPU Fan Connectors (CPUFAN1). Figure 2.8 CPU Fan Connectors (CPUFAN1). Front Panel Connectors (JFP1). Figure 2.9 Front Panel Connectors (JFP1).                                                                                                                                                                                                                       | 12 13 14 15 15 15 16 16 17 17 17                         |

|         | 2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9         | IDE Connector (IDE1) Figure 2.1 PCI-7031 IDE1 location Floppy Drive Connector (FDD1) Figure 2.2 PCI-7031 FDD1 location Parallel Port (LPT1) Figure 2.3 PCI-7031 LPT1 location VGA Connector (VGA1) Figure 2.4 VGA Connector (VGA1) Serial Ports (COM12) Figure 2.5 Serial Ports (COM12) PS/2 Keyboard/Mouse Connector (KBMS1) Figure 2.6 PS/2 Keyboard/Mouse Connector (KBMS1) External Keyboard Pin Header (KBMS2) Figure 2.7 External Keyboard Connector (KBMS2) CPU Fan Connectors (CPUFAN1) Figure 2.8 CPU Fan Connectors (CPUFAN1) Front Panel Connectors (JFP1) Figure 2.9 Front Panel Connectors (JFP1) 2.10.1 ATX Power Button (JFP1 Pin 1~2) 2.10.2 Reset (JFP1 Pin 3~4)                                                                                                                                                                         | 12 13 14 15 15 15 16 16 17 17 17 17                      |

|         | 2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9         | IDE Connector (IDE1) Figure 2.1 PCI-7031 IDE1 location Floppy Drive Connector (FDD1) Figure 2.2 PCI-7031 FDD1 location  Parallel Port (LPT1) Figure 2.3 PCI-7031 LPT1 location  VGA Connector (VGA1) Figure 2.4 VGA Connector (VGA1)  Figure 2.5 Serial Ports (COM12) Figure 2.5 Serial Ports (COM12)  PS/2 Keyboard/Mouse Connector (KBMS1) Figure 2.6 PS/2 Keyboard/Mouse Connector (KBMS1)  External Keyboard Pin Header (KBMS2) Figure 2.7 External Keyboard Connector (KBMS2)  CPU Fan Connectors (CPUFAN1) Figure 2.8 CPU Fan Connectors (CPUFAN1) Front Panel Connectors (JFP1) Figure 2.9 Front Panel Connectors (JFP1) 2.10.1 ATX Power Button (JFP1 Pin 1~2) 2.10.2 Reset (JFP1 Pin 3~4) 2.10.3 Suspend LED (JFP1 Pin 5~6)                                                                                                                      | 12 13 14 15 15 15 16 16 16 17 17 17 17                   |

|         | 2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9         | IDE Connector (IDE1) Figure 2.1 PCI-7031 IDE1 location Floppy Drive Connector (FDD1) Figure 2.2 PCI-7031 FDD1 location Parallel Port (LPT1) Figure 2.3 PCI-7031 LPT1 location VGA Connector (VGA1) Figure 2.4 VGA Connector (VGA1) Serial Ports (COM12) Figure 2.5 Serial Ports (COM12) PS/2 Keyboard/Mouse Connector (KBMS1) Figure 2.6 PS/2 Keyboard/Mouse Connector (KBMS1) External Keyboard Pin Header (KBMS2) Figure 2.7 External Keyboard Connector (KBMS2) CPU Fan Connectors (CPUFAN1) Figure 2.8 CPU Fan Connectors (CPUFAN1) Front Panel Connectors (JFP1) Figure 2.9 Front Panel Connectors (JFP1) 2.10.1 ATX Power Button (JFP1 Pin 1~2) 2.10.2 Reset (JFP1 Pin 3~4) 2.10.3 Suspend LED (JFP1 Pin 5~6) 2.10.4 Power LED and keyboard lock connector (JFP1 Pin 7~8)                                                                           | 12 13 14 15 15 15 16 16 16 17 17 17 17 18 18             |

|         | 2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9         | IDE Connector (IDE1) Figure 2.1 PCI-7031 IDE1 location Floppy Drive Connector (FDD1) Figure 2.2 PCI-7031 FDD1 location Parallel Port (LPT1) Figure 2.3 PCI-7031 LPT1 location VGA Connector (VGA1) Figure 2.4 VGA Connector (VGA1) Serial Ports (COM12) Figure 2.5 Serial Ports (COM12) Figure 2.6 PS/2 Keyboard/Mouse Connector (KBMS1) Figure 2.6 PS/2 Keyboard/Mouse Connector (KBMS1) External Keyboard Pin Header (KBMS2) Figure 2.7 External Keyboard Connector (KBMS2) CPU Fan Connectors (CPUFAN1) Figure 2.8 CPU Fan Connectors (CPUFAN1) Figure 2.9 Front Panel Connectors (JFP1) 2.10.1 ATX Power Button (JFP1 Pin 1~2) 2.10.2 Reset (JFP1 Pin 3~4) 2.10.3 Suspend LED (JFP1 Pin 5~6) 2.10.4 Power LED and keyboard lock connector (JFP1 Pin 7~8) Table 2.1: ATX power supply LED status (No support for AT                                    | 12 13 14 15 15 15 16 16 17 17 17 17 18 18 pow-           |

|         | 2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9         | IDE Connector (IDE1) Figure 2.1 PCI-7031 IDE1 location Floppy Drive Connector (FDD1) Figure 2.2 PCI-7031 FDD1 location Parallel Port (LPT1) Figure 2.3 PCI-7031 LPT1 location VGA Connector (VGA1) Figure 2.4 VGA Connector (VGA1) Serial Ports (COM12) Figure 2.5 Serial Ports (COM12) PS/2 Keyboard/Mouse Connector (KBMS1) Figure 2.6 PS/2 Keyboard/Mouse Connector (KBMS1) External Keyboard Pin Header (KBMS2) Figure 2.7 External Keyboard Connector (KBMS2) CPU Fan Connectors (CPUFAN1) Figure 2.8 CPU Fan Connectors (CPUFAN1) Front Panel Connectors (JFP1) Figure 2.9 Front Panel Connectors (JFP1) 2.10.1 ATX Power Button (JFP1 Pin 1~2) 2.10.2 Reset (JFP1 Pin 3~4) 2.10.3 Suspend LED (JFP1 Pin 5~6) 2.10.4 Power LED and keyboard lock connector (JFP1 Pin 7~8) Table 2.1: ATX power supply LED status (No support for AT er)             | 12 13 14 15 15 15 16 16 17 17 17 17 18 18 pow 18         |

|         | 2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10 | IDE Connector (IDE1) Figure 2.1 PCI-7031 IDE1 location  Floppy Drive Connector (FDD1) Figure 2.2 PCI-7031 FDD1 location  Parallel Port (LPT1) Figure 2.3 PCI-7031 LPT1 location  VGA Connector (VGA1) Figure 2.4 VGA Connector (VGA1)  Serial Ports (COM12) Figure 2.5 Serial Ports (COM12)  PS/2 Keyboard/Mouse Connector (KBMS1) Figure 2.6 PS/2 Keyboard/Mouse Connector (KBMS1)  External Keyboard Pin Header (KBMS2) Figure 2.7 External Keyboard Connector (KBMS2)  CPU Fan Connectors (CPUFAN1) Figure 2.8 CPU Fan Connectors (CPUFAN1)  Front Panel Connectors (JFP1) Figure 2.9 Front Panel Connectors (JFP1)  2.10.1 ATX Power Button (JFP1 Pin 1~2)  2.10.2 Reset (JFP1 Pin 3~4)  2.10.3 Suspend LED (JFP1 Pin 5~6)  2.10.4 Power LED and keyboard lock connector (JFP1 Pin 7~8) Table 2.1: ATX power supply LED status (No support for AT er) | 12 13 14 15 15 15 16 16 17 17 17 17 17 18 18 18 18 18 18 |

|         | 2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9         | IDE Connector (IDE1) Figure 2.1 PCI-7031 IDE1 location Floppy Drive Connector (FDD1) Figure 2.2 PCI-7031 FDD1 location Parallel Port (LPT1) Figure 2.3 PCI-7031 LPT1 location VGA Connector (VGA1) Figure 2.4 VGA Connector (VGA1) Serial Ports (COM12) Figure 2.5 Serial Ports (COM12) PS/2 Keyboard/Mouse Connector (KBMS1) Figure 2.6 PS/2 Keyboard/Mouse Connector (KBMS1) External Keyboard Pin Header (KBMS2) Figure 2.7 External Keyboard Connector (KBMS2) CPU Fan Connectors (CPUFAN1) Figure 2.8 CPU Fan Connectors (CPUFAN1) Front Panel Connectors (JFP1) Figure 2.9 Front Panel Connectors (JFP1) 2.10.1 ATX Power Button (JFP1 Pin 1~2) 2.10.2 Reset (JFP1 Pin 3~4) 2.10.3 Suspend LED (JFP1 Pin 5~6) 2.10.4 Power LED and keyboard lock connector (JFP1 Pin 7~8) Table 2.1: ATX power supply LED status (No support for AT er)             | 12 13 14 15 15 15 16 16 17 17 17 17 17 18 18 18 18 18 18 |

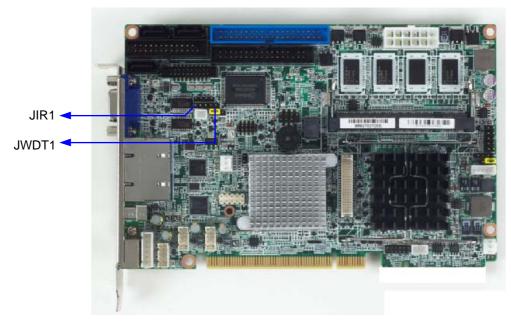

|         |      |                                        | Table 2.2: Watchdog timer output (JWDT1)            | 19       |

|---------|------|----------------------------------------|-----------------------------------------------------|----------|

|         |      | 2.11.2                                 | 2 Infrared Connector (JIR1)                         | 19       |

|         | 2.12 | Dual (                                 | Giga LAN RJ45 connector (LAN12)                     | 20       |

|         |      |                                        | Figure 2.11Dual Giga LAN RJ45 connector (LAN12)     | 20       |

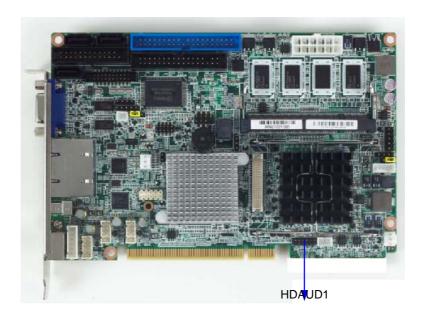

|         | 2.13 | High [                                 | Definition Audio Interface (HDAUD1)                 | 20       |

|         |      |                                        | Figure 2.12High Definition Audio Interface (HDAUD1) | 20       |

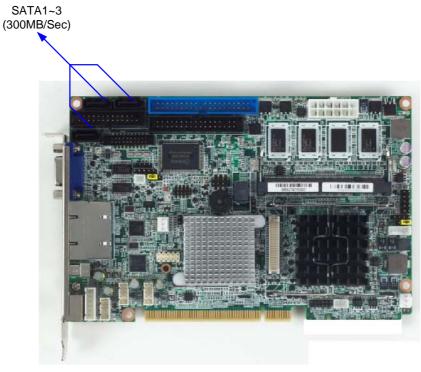

|         | 2.14 | Serial                                 | ATA interface (SATA1 ~ SATA3)                       | 21       |

|         |      |                                        | Figure 2.13Serial ATA interface (SATA1 ~ SATA3)     | 21       |

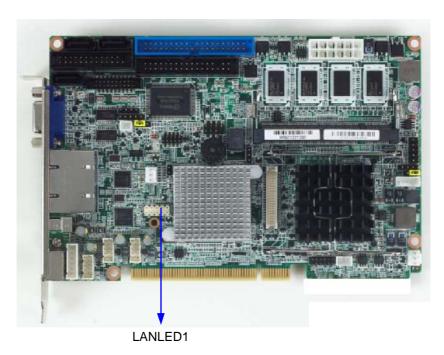

|         | 2.15 | LAN1                                   | and LAN2 LED connector (LANLED1)                    | 21       |

|         |      |                                        | Figure 2.14LAN1 and LAN2 LED connector (LANLED1)    | 21       |

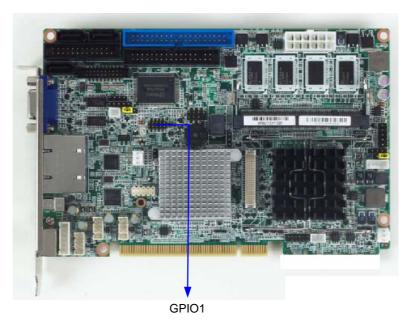

|         | 2.16 | GPIO                                   | header (GPIO1)                                      |          |

|         |      |                                        | Figure 2.15 GPIO header (GPIO1)                     | 22       |

|         | 2.17 | CMOS                                   | S clear (CMOS1)                                     |          |

|         |      |                                        | Table 2.3: CMOS (CMOS1)                             |          |

|         | 2.18 |                                        | Feature connector(ATXF1)                            |          |

|         | 2.19 | ATX p                                  | ower control connector (ATX1)                       | 24       |

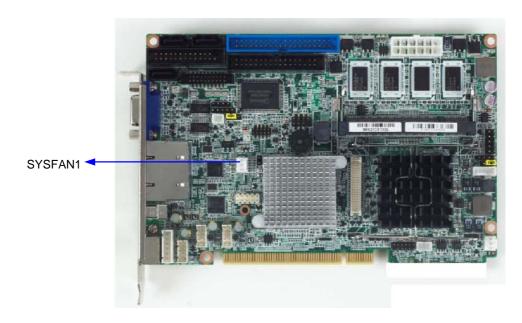

|         | 2.20 | Syste                                  | m FAN connector (SYSFAN1)                           | 25       |

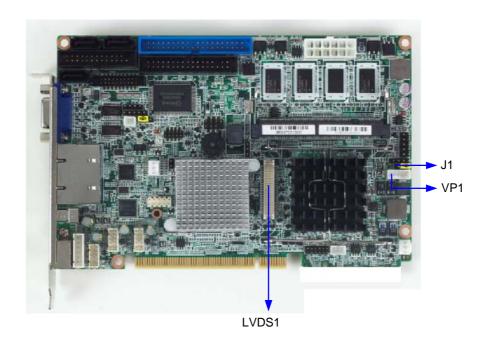

|         | 2.21 | LVDS                                   | Signal and Power Connectors (LVDS1/VP1)             | 25       |

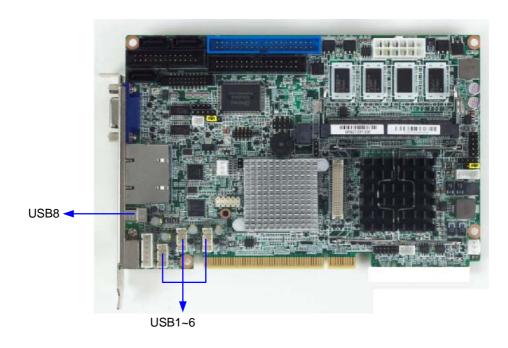

|         | 2.22 | USB F                                  | Ports (USB 1~6 & 8)                                 | 26       |

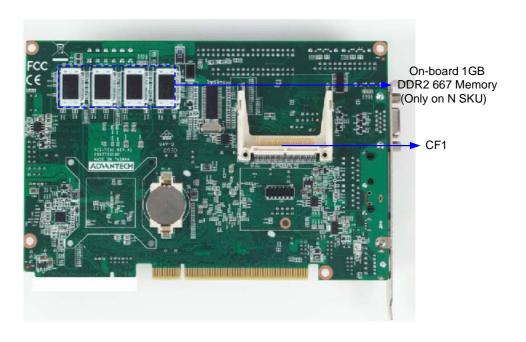

|         | 2.23 | CF Ca                                  | ard Socket                                          | 26       |

|         | 2.24 | Low P                                  | in Count Device Connection Pin Header               | 27       |

|         |      |                                        |                                                     |          |

| Chapter | 3    | $\Delta M$                             | I BIOS Setup                                        | 20       |

| Onapici | 9    | /\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | i bioo octup                                        | . 25     |

|         |      |                                        | Figure 3.1 Setup Program Initial Screen             | 30       |

|         | 3.1  | Enteri                                 | ng Setup                                            |          |

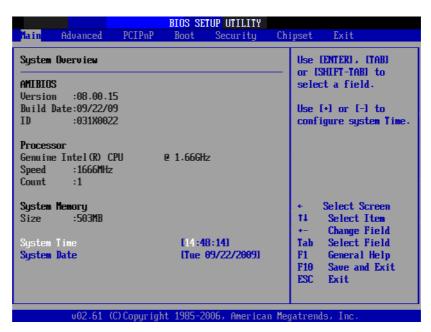

|         | 3.2  |                                        | Setup                                               |          |

|         |      |                                        | Figure 3.2 Main Setup Screen                        |          |

|         |      | 3.2.1                                  | System time / System date                           |          |

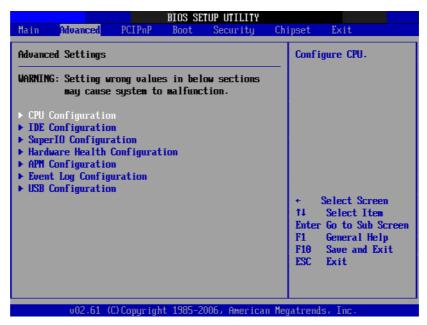

|         | 3.3  | Advar                                  | nced BIOS Features Setup                            |          |

|         |      |                                        | Figure 3.3 Advanced BIOS Features Setup Screen      | 32       |

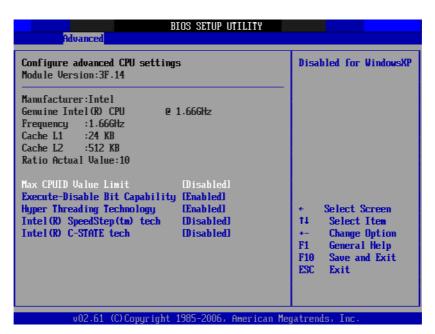

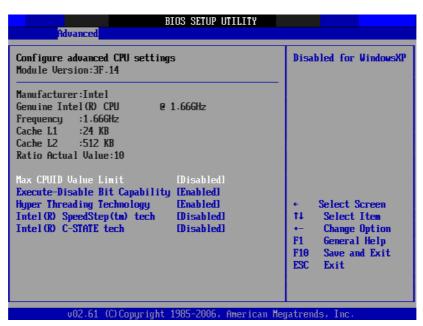

|         |      | 3.3.1                                  | CPU Configuration                                   | 33       |

|         |      |                                        | Figure 3.4 CPU Configuration Settings               | 33       |

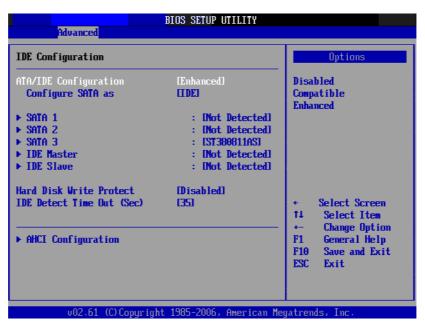

|         |      | 3.3.2                                  | IDE Configuration                                   |          |

|         |      |                                        | Figure 3.5 IDE Configuration                        |          |

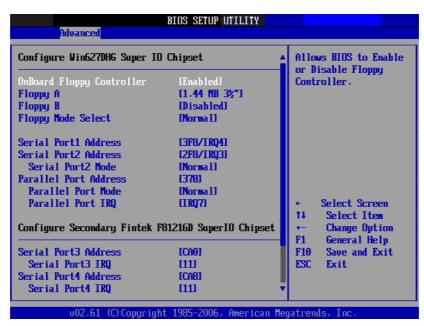

|         |      | 3.3.3                                  | ,                                                   |          |

|         |      |                                        | Figure 3.6 Super I/O Configuration                  |          |

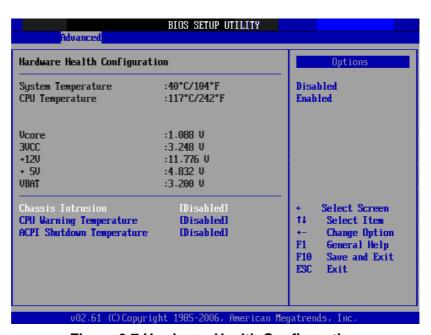

|         |      | 3.3.4                                  | Hardware Health Function                            |          |

|         |      | 0.05                                   | Figure 3.7 Hardware Health Configuration.           |          |

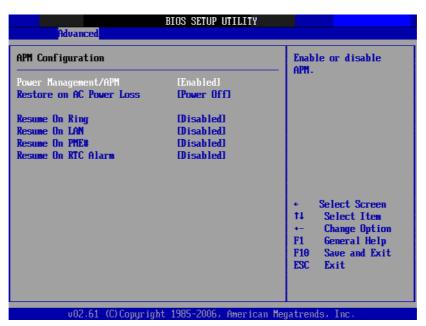

|         |      | 3.3.5                                  | APM ConfigurationFigure 3.8 APM Configuration       |          |

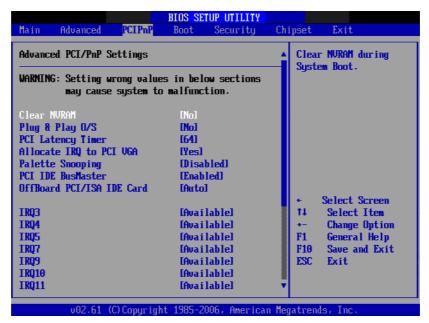

|         | 3.4  | DCI/D                                  | · ·                                                 |          |

|         | 3.4  | PCI/P                                  | NP Setup Figure 3.9 PCI/PNP Setup                   | 30<br>20 |

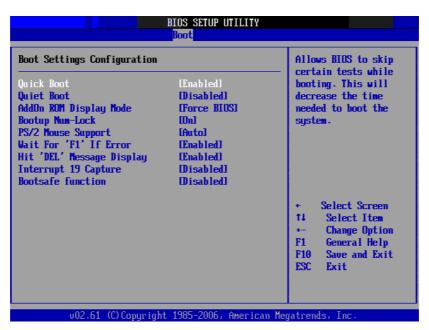

|         | 3.5  | Poot 9                                 | Setup Utility                                       |          |

|         | 3.5  | D001 C                                 | Figure 3.10Boot Settings Configuration              |          |

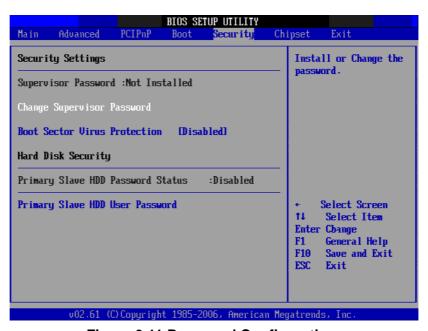

|         | 3.6  | Socur                                  | ity Setup                                           |          |

|         | 3.0  | Secui                                  | Figure 3.11Password Configuration                   |          |

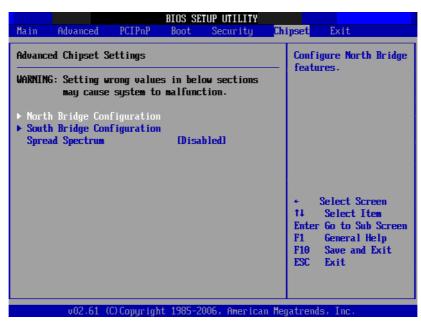

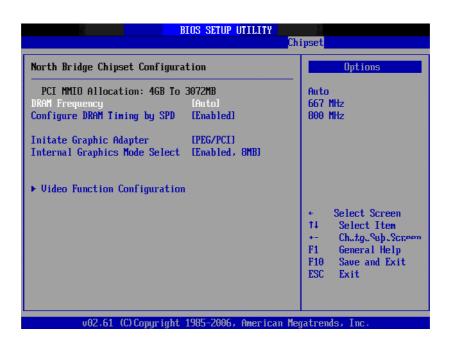

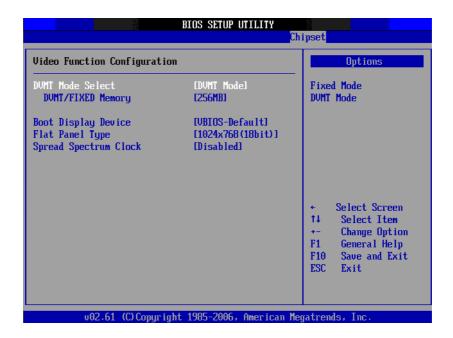

|         | 3.7  | Δdvar                                  | nced Chipset Settings                               |          |

|         | 3.7  | Auvai                                  | Figure 3.12Advanced Chipset Settings                |          |

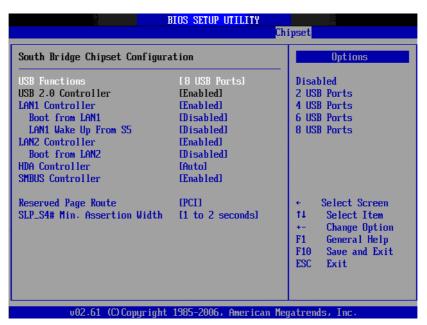

|         |      |                                        | Figure 3.13Souh Bridge Configuration                |          |

|         | 3.8  | Fyit (                                 | ptions                                              |          |

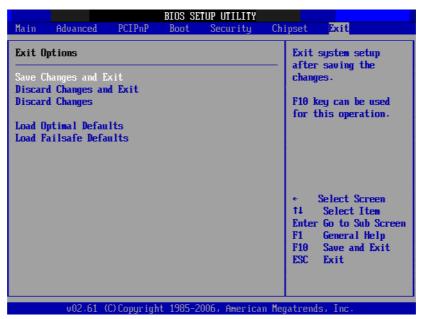

|         | 5.0  | LAILO                                  | Figure 3.14Exit Options                             |          |

|         |      | 3.8.1                                  | Save Changes and Exit                               |          |

|         |      | 3.8.2                                  | Discard Changes and Exit                            |          |

|         |      | 3.8.3                                  | Discard Changes                                     |          |

|         |      | 3.8.4                                  | Load Optimal Defaults                               |          |

|         |      | 3.8.5                                  | Load Failsafe Defaults                              |          |

|         |      |                                        |                                                     |          |

| Chapter | 4          | Value-Added Software Services                                        | 47   |

|---------|------------|----------------------------------------------------------------------|------|

|         | 4.1        | Value-Added Software Services                                        | 48   |

|         | _          | ·                                                                    |      |

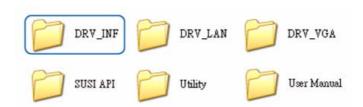

| Chapter | 5          | Chipset Software Installation Utility                                | / 51 |

|         | 5.1        | Before You Begin                                                     | 52   |

|         | 5.2<br>5.3 | Introduction                                                         |      |

|         | 5.5        | ,                                                                    |      |

| Chapter | 6          | Integrated Graphic Device Setup                                      | 55   |

|         | 6.1        | Introduction                                                         |      |

|         | 6.2        | Windows XP/XP Embedded/CE Driver Setup                               | 56   |

| Chapter | 7          | LAN Configuration                                                    | 57   |

| -       | 7.1        | Introduction                                                         | 58   |

|         | 7.2        | Installation                                                         |      |

|         | 7.3        | Windows XP/XP Embedded/CE Driver Setup                               | 58   |

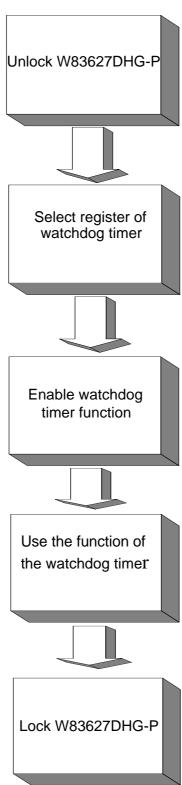

| Appendi | хА         | Programming the Watchdog Timer                                       | 59   |

|         | A.1        | Watchdog Timer                                                       | 60   |

|         |            | A.1.1 Watchdog Timer Overview                                        |      |

|         |            | A.1.2 Reset/ Interrupt Selection                                     |      |

|         |            | Table A.1: Watchdog Timer Registers                                  |      |

|         |            | A.1.4 Example Program                                                | 63   |

| Appendi | хВ         | I/O Pin Assignments                                                  | 67   |

|         | B.1        | Front Panel Connectors (JFP1)                                        | 68   |

|         | 5.0        | Table B.1: Front Panel Connectors (JFP1)                             |      |

|         | B.2        | USB Ports (USB12/USB34/USB56)                                        |      |

|         | B.3        | IR Connector (JIR1)                                                  |      |

|         |            | Table B.3: IR Connector (JIR1)                                       | 69   |

|         | B.4        | Serial Ports (COM12)                                                 |      |

|         | B.5        | PS/2 Keyboard / Mouse connector (KBMS2)                              |      |

|         |            | Table B.5: PS/2 Keyboard / Mouse connector (KBMS2)                   | 70   |

|         | B.6        | LAN LED connector (LANLED1/LANLED2)                                  |      |

|         | B.7        | ATX Feature connector(ATXF1)                                         |      |

|         |            | Table B.7: ATX Feature connector(ATXF1)                              | 71   |

|         | B.8        | CPU FAN connector (CPUFAN1)                                          |      |

|         | B.9        | Table B.8: CPU FAN connector (CPUFAN1)System FAN connector (SYSFAN1) |      |

|         | ь.э        | Table B.9: System FAN connector (SYSFAN1)                            |      |

|         | B.10       | Audio Interface Connector (HDAUD1)                                   | 72   |

|         |            | Table B.10:Audio Interface Connector (HDAUD1)                        | 72   |

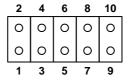

| B.11       | GPIO Header (GPIO1)                           | 72 |

|------------|-----------------------------------------------|----|

|            | Table B.11:GPIO Header (GPIO1)                | 72 |

| B.12       | LVDS Connector (LVDS1)                        | 73 |

|            | Table B.12:LVDS Connector (LVDS1)             | 73 |

| B.13       | LCD Inverter Connector (VP1)                  | 73 |

|            | Table B.13:LCD Inverter Connector (VP1)       | 73 |

| B.14       | SM Bus Connector (SMBUS1)                     | 74 |

|            | Table B.14:SM Bus Connector (SMBUS1)          | 74 |

| B.15       | Low Pin Count Header (LPC1)                   | 74 |

|            | Table B.15:Low Pin Count Header (LPC1)        | 74 |

| B.16       | ATX Power Control Connector (ATX1)            | 75 |

|            | Table B.16:ATX Power Control Connector (ATX1) | 75 |

| B.17       | VGA Connector (VGA1)                          |    |

|            | Table B.17:VGA Connector (VGA1)               | 75 |

| Appendix C | Programming the GPIO                          | 77 |

| C.1        | Supported GPIO Register                       | 78 |

|            | C.1.1 GPIO Registers                          |    |

|            | C.1.2 GPIO Example Program-1                  | 79 |

# Chapter

Hardware Configuration

#### 1.1 Introduction

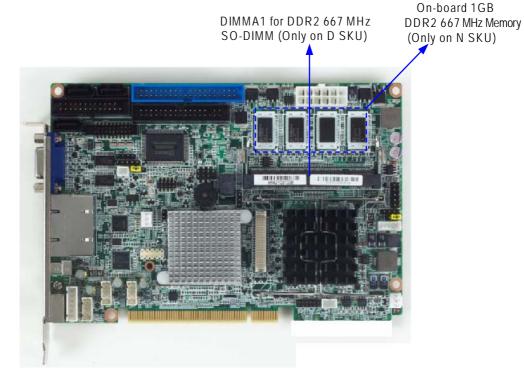

PCI-7031 is an Atom dual-core D510 / fanless N450 CPU based PCI-interface half-size PICMG single board computer. With high performance Atom D510 dual-core computing power, it is ideal for intense data or graphic processing applications; with fanless Atom N450 CPU and on-board memory feature, it has ultra high reliability to resist heat, dust, vibration and shock in any application environment.

PCI-7031 is designed with an Intel® Atom™ D510/N450 CPU and ICH8M I/O control hub. The Atom D510 dual core CPU brings new generation computing capability into the half-size SBC application field. Compact size, low power consumption (Total power consumption ≤17.796 W) and dual-core parallel computing power and maximum 2 GB of DDR2 667 MHz memory capacity makes the PCI-7031D a powerful small form-factor computer platform for modern industrial applications that require high computing power. The fanless Atom N450 CPU (Total power consumption ≤ 15.264 W) and on-board memory design eliminate moving fan parts and memory socket connections; this makes PCI-7031N ultra reliable to conduct its mission under various kinds of high-temperature, vibrating, shocking and dusty harsh environments.

PCI-7031 has an integrated graphic core of Intel Embedded Gen3.5+ graphic technology with 224 MB shared memory. This feature makes PCI-7031 is capable of handling complex and intense 2D/3D graphic processing without an add-on graphic card; its VGA and LVDS dual video outputs also makes it suitable for applications requiring dual display or digital panel display capabilities.

PCI-7031 is rich in I/O interfaces: it has three SATA ports (300 MB/sec) for mainstream SSD (solid state disk), HDD, and ODD connections, one legacy IDE port for the ODD connection. It also has a CF socket to support an economical, easy-tomaintain SSD device. Additionally, the dual Gigabit Ethernet LANs with teaming functions offer strong networking capability; the two serial ports (COM ports) can be used as reliable legacy device control interfaces.

#### 1.2 Features

- Complies with PICMG<sup>®</sup> 1.0